DG645数字脉冲延迟发生器

·4路脉冲信号,8路延时输出

·< 25ps RMS抖动

·触发速率10MHz

·精度率发生器

·易于与80MHz模式锁定激光器

·快速过渡时间

·加热晶体或Rb时基(opt.)

·以太网、GPIB、RS-232接口

·4路脉冲信号,8路延时输出

·< 25ps RMS抖动

·触发速率10MHz

·精度率发生器

·易于与80MHz模式锁定激光器

·快速过渡时间

·加热晶体或Rb时基(opt.)

·以太网、GPIB、RS-232接口

DG645

DG645 是一款多功能数字延迟/脉冲发生器,可提供精确定义的脉冲,重复频率高达 10 MHz。

延迟发生器时序

时序图 |

所有数字延迟发生器都通过计算快速时钟(通常为 100 MHz)的周期来测量时间间隔。大多数数字延迟发生器还具有较短的可编程模拟延迟,以实现比时钟周期更精细的时间间隔。不幸的是,如果触发器与时钟不同步,则可能会出现一个时钟周期的时序不确定性(通常为 10 ns)。

DG645 通过测量触发器相对于内部时钟的时序并补偿模拟延迟来消除时序不确定性。这种方法将抖动降低了大约 100 倍,并允许内部速率发生器以任何速率运行,而不仅仅是时钟频率的约数。

触发

DG645 有多种触发模式。具有小于 100 ps 周期抖动的内部速率发生器可以设置为 100 µHz 至 10 MHz,分辨率为 1 µHz。具有可调阈值和斜率的外部触发输入可以触发定时周期、周期突发或单次触发。可以通过按键触发单次射击。线路触发器与交流电源同步运行。

DG645 通过触发释抑和预分频功能支持许多复杂的触发要求。

触发释抑设置连续触发之间的最短时间。如果您的应用程序中的触发事件产生显着的噪声瞬变,在生成下一个触发之前需要时间衰减,这将非常有用。触发释抑也可用于以输入触发速率的约数来触发 DG645。

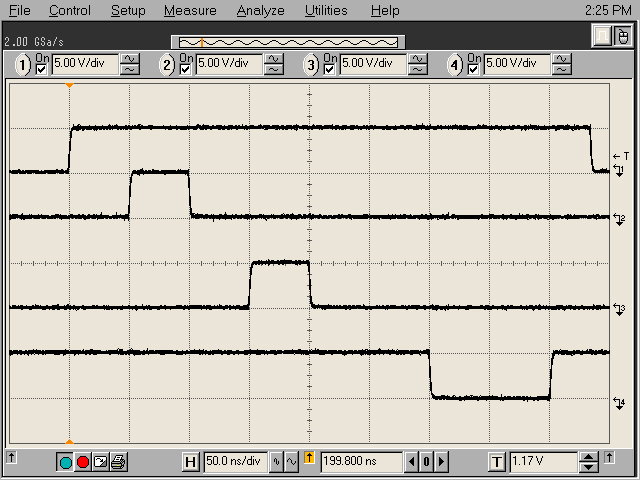

前面板输出 |

触发预分频使 DG645 能够与更快的源同步触发,但触发频率是原始触发频率的约数。例如,DG645 可以在 1 kHz 下触发,但与以 80 MHz 运行的锁模激光器同步,通过将触发输入预缩放 80,000。此外,DG645 还为每个前面板输出包含一个单独的预分频器,使每个输出能够以触发速率的约数工作。

前面板输出

有五个前面板输出:T 0、AB、CD、EF 和 GH。T 0输出在定时周期内被置位。T 0 的前沿是零时间参考。编程延迟(A、B、C、D、E、F、G 和 H)设置为 0 秒到 2000 秒,分辨率为 5 ps,以控制四个脉冲输出的前沿和后沿的时序。

每个前面板输出可驱动 50 Ω 负载并具有 50 Ω 源阻抗。输出幅度可设置为 0.5 至 5.0 V,输出偏移范围可超过 ±2 VDC,以提供几乎任何逻辑电平(NIM、ECL、PECL、CMOS 等)。在任何输出幅度下,输出转换时间都小于 2 ns。

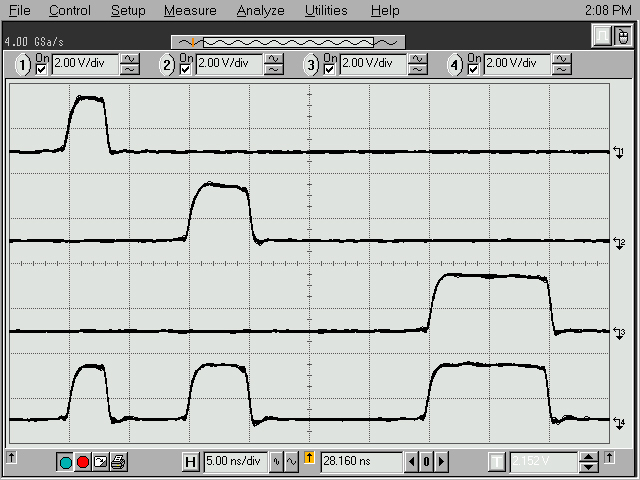

组合输出 |

后面板输出

可选的后面板输出可用于支持各种应用。选项 1 在 5 V 逻辑电平下提供 T 0输出和八个编程延迟(A、B、C、D、E、F、G 和 H),转换时间小于 1 ns。选项 2 提供这些相同的输出,但作为 30 V、100 ns 脉冲,转换时间小于 5 ns,用于高噪声环境中的时序分布。选项 3 提供 8 个组合输出,可提供 5 V 逻辑电平的 1 到 4 个脉冲,转换时间小于 1 ns。每个输出都有一个 50 Ω 的源阻抗。

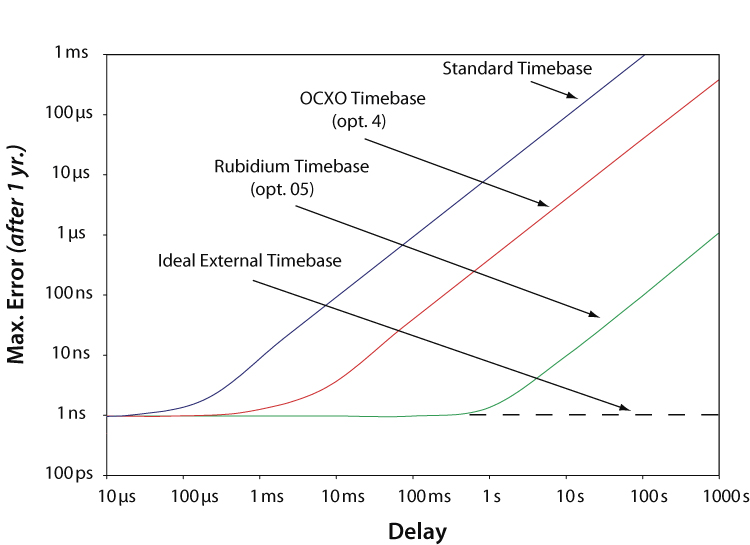

时基

标准时基的精度为 5 ppm,抖动为

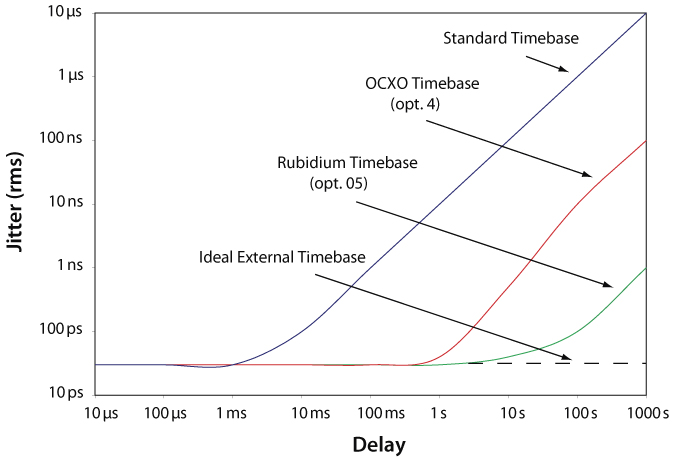

对于标准时基,1 s 延迟的计时误差可高达 5 µs,OCXO 时基为 200 ns,但铷时基仅为 500 ps(均在校准一年后)。

时序误差与延迟 |

对于短延迟,抖动通常为 20 ps。然而,对于 1 s 的延迟,标准时基会产生高达 10 ns 的抖动,而可选时基会产生不到 10 ps 的额外抖动。

快速上升时间模块

DG645 前面板输出的转换时间小于 2 ns。SRD1 是一种附件,内置于直插式 BNC 连接器中,可将前面板输出的上升时间缩短至 100 ps 以下。前面板最多可连接五个 SRD1,以减少所有输出的上升时间。

抖动与延迟 |

DG645 规格

延误

频道4 个独立脉冲控制位置和宽度。8 个延迟通道可供选择。

(见下面的输出选项)

范围0 到 2000 秒

解决5 皮秒

准确性1 ns + (时基误差 × 延迟)

抖动 (rms)

分机。触发。到任何输出

T 0到任何输出

25 ps + (时基抖动 × 延迟)

15 ps + (时基抖动 × 延迟)

触发延迟85 ns(外部触发到 T 0输出)

时基

标准水晶

抖动10 -8秒/秒

稳定2 x 10 -6 (20 °C 至 30 °C)

老化5 ppm/年

选择。4 OCXO

抖动10 -11秒/秒

稳定2 x 10 -9 (20 °C 至 30 °C)

老化0.2 ppm/年

选择。5 铷

抖动10 -11秒/秒

稳定2 x 10 -10(20 °C 至 30 °C)

老化0.0005 ppm/年

外部输入10 MHz ± 10 ppm,正弦 >0.5 Vpp,

1 kΩ 阻抗

输出10 MHz,2 Vpp 输入 50 Ω

外部触发

速度DC 至 1/(100 ns + 最长延迟)。

最大 10 MHz

临界点±3.50 伏直流

坡在上升沿或下降沿触发

阻抗1 兆欧 + 15 pF

内部速率发生器

触发模式连拍、线拍或单拍

速度100 µHz 至 10 MHz

解决1 微赫兹

准确性与时基相同

抖动 (rms)<25 ps(10 MHz/N 触发率)

<100 ps(其他触发率)

突发发生器

触发到第一个 T 0

范围

分辨率

0 到 2000 秒

5 ps

脉冲之间的周期

范围

分辨率

100 ns 至 42.9 s

10 ns

每个突发的延迟周期1 至 2 32 - 1

输出(T 0、AB、CD、EF 和 GH)

源阻抗50Ω

过渡时间<2 纳秒

过冲<100 mV + 10 % 的脉冲幅度

抵消±2V

振幅0.5 至 5.0 V(电平 + 偏移 <6.0 V)

准确性100 mV + 5 % 脉冲幅度

一般的

计算机接口GPIB (IEEE-488.2)、RS-232 和以太网。所有仪器功能都可以通过接口进行控制。

非易失性存储器可以存储和调用九组仪器配置。

力量<100 W,90 至 264 VAC,47 Hz 至 63 Hz

方面8.5" × 3.5" × 13" (WHL)

重量9 磅。

保修单一年零件和人工材料和工艺缺陷

输出选项

选项 1(延迟输出)

输出数量8 个(后面板 BNC)

输出T 0 , A, B, C, D, E, F, G 和 H

源阻抗50Ω

过渡时间<1 纳秒

过冲<100 毫伏

等级+5 V CMOS 逻辑

脉冲特性

上升沿

下降沿

在最长延迟后 25 ns 编程延迟

选项 2(高压输出)

输出数量8 个(后面板 BNC)

输出T 0 , A, B, C, D, E, F, G 和 H

源阻抗50Ω

过渡时间<5 纳秒

级别0 至 30 V 进入高阻抗,0 至 15 V 进入 50 Ω(幅度降低 1 %/kHz)

脉冲特性

上升沿

下降沿

在上升沿后 100 ns 的 编程延迟

选项 3(组合输出)

输出数量8 个(后面板 BNC)

输出T 0 , AB, CD, EF, GH, (AB+CD), (EF+GH), (AB+CD+EF), (AB+CD+EF+GH)

源阻抗50Ω

过渡时间<1 纳秒

过冲<100 mV + 10 % 的脉冲幅度

脉冲特性

T 0 , AB, CD, EF, GH延迟之间的时间逻辑高

(AB+CD), (EF+GH)由给定通道的逻辑或创建的两个脉冲

(AB+CD+EF)由给定通道的逻辑或创建的三个脉冲

(AB+CD+EF+GH)由给定通道的逻辑或创建的四个脉冲

选项 SRD1(快速上升时间模块)

上升时间<100 皮秒

秋季时间<3 纳秒

抵消-0.8 V 至 -1.1 V

振幅0.5V 至 5.0V

加载50Ω